お知らせ

- トップ

- お知らせ

3次元トポロジカル絶縁体面内p-n接合の動作に成功 -低電力消費素子への応用に期待-

東北大学大学院理学研究科の田邉洋一助教、ダウノックハン博士(当時東北大学大学院理学研究科物理学専攻博士課程3年)、同原子分子材料科学高等研究機構(WPI-AIMR)の谷垣勝己教授は、3次元トポロジカル絶縁体Bi2-xSbxTe3-ySeyの表面を用いた新しい原理の電流/スピン流(*1)の制御機構の動作に成功しました。

3次元トポロジカル絶縁体は、物質内部は絶縁体で電流を通さず、表面には金属状態が存在し、電流を流すことのできる新しい絶縁体です。この表面状態は質量ゼロのディラック状態(*2)として知られており、非常に低散逸な電流とスピン流の生成が可能であることから省エネ素子への応用に向けた研究が行われています。しかし3次元トポロジカル絶縁体では、電流の担い手が電子の物質(n型)と正孔の物質(p型)を組み合わせるとその境界(p-n接合)において、従来のシリコンなどとは異なる原理に基づいた電流とスピン流の制御が起こることが理論から予想されていましたが、これまで実験からは観測されていませんでした。

今回研究グループは、n型の3次元トポロジカル絶縁体Bi2-xSbxTe3-ySey大型薄膜を物理気相蒸着(*3)という非常に簡便で低コストな手法を用いて作成し、さらに、有機分子を蒸着するだけという容易な手法を用いて薄膜の半分の領域に正孔を注入することによって3次元トポロジカル絶縁体p-n接合の作製に成功しました。さらに、この薄膜を用いて電界効果型トランジスタ(*4)を作製し、薄膜内部の電子数を変化させたところ、p-n接合の制御によって電気抵抗率が劇的に変化することを観測しました。本成果から、トポロジカル絶縁体を用いた電子デバイスにおいて鍵となるp-n接合の作製と制御が可能となったことから、省エネ素子への応用が期待されます。

本研究は世界トップレベル研究拠点プログラム(WPI)の支援を受けて行われたもので、英国のオンライン科学雑誌「Nature Communications」に12月9日(英国時間)オンライン掲載されます。

研究の背景

3次元トポロジカル絶縁体は、物質内部は絶縁体で電流を通さず、表面には金属状態が存在し、電流を流すことのできる新しい絶縁体です。この表面状態は質量ゼロのディラック状態であり、非常に低散逸な電流輸送が可能であることが知られています。このような状態は、2010年にノーベル賞の対象となった炭素の2次元シートから成るグラフェンにおいて良く知られていますが、3次元トポロジカル絶縁体においては、電子のミクロな自転運動の軸であるスピンが運動方向に対して揃う性質を持つことから、低散逸な電流/スピン流を利用した省エネデバイスの実現が期待されています。一方で、トポロジカル絶縁体の表面は金属であることから、従来のシリコンなどと同様に電子の存在しない状態と存在する状態を切り替えることによる素子の制御ができないという問題がありました。3次元トポロジカル絶縁体では、電流の担い手が電子の物質(n型)と正孔(p型)の物質において運動の方向に対してスピンの偏極方向が反転するという性質があり、これらが接する境界(p-n接合)において電流の反射、スピン流の増幅、スピン流のフィルタリングが起こることが予想されています。このため、トポロジカルp-n接合を用いた低散逸な電流/スピン流の制御素子の実現が期待されていましたが、これまで実現はされていませんでした。

研究の内容

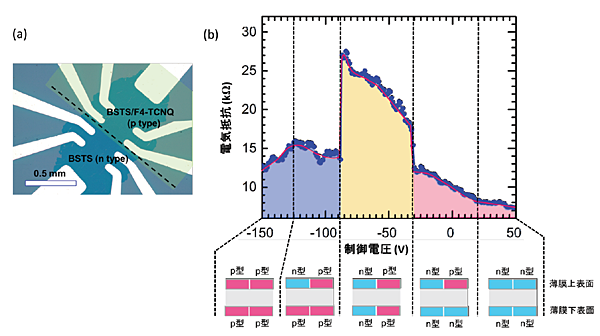

本研究では、バルク絶縁性の高いn型の3次元トポロジカル絶縁体Bi2-xSbxTe3-ySey薄膜を使用して電界効果トランジスタを作製し、これらをトポロジカルp-n接合の作製に使用しました。n型の3次元トポロジカル絶縁体薄膜を用いてp-n接合を作製する場合、薄膜の一部領域で電流の担い手をp型に変える必要があります。今回、低温で蒸着可能でかつ高価な元素を含まない有機分子に着目し、有機分子とトポロジカル絶縁体の内部から電子を取り出すのに必要なエネルギーの違いに基づいて起こる電子と正孔のやり取りを利用することによって、図2(a)に示すようなp-n接合素子を作製しました。

図2(b)のp-n接合素子の振る舞いからは、Bi2-xSbxTe3-ySey薄膜の上下表面にp-n接合が形成された場合に急激な電気抵抗の増大が起こることを観測しました。理論からは、トポロジカルp-n接合界面において電流の担い手である電子が強く反射されるために電気抵抗の増大が起こることが予想されていることから、トポロジカルp-n接合における整流作用と一致する振る舞いです。一方で、電気抵抗の増大が理論の予測と比較して急激であることから、ディラック状態以外の表面状態がトポロジカルp-n接合の高い抵抗の状態のオン/オフの切り替えに寄与していると考えられます。

今後の展開

3次元トポロジカル絶縁体を用いたp-n接合素子は、3次元トポロジカル絶縁体の表面の低散逸な電流/スピン流を制御するうえで鍵となる電子素子です。本成果から、トポロジカルp-n接合の形成により、接合界面での電子の反射として理解できる高抵抗状態が出現することが示されました。今後デバイスをより改良することで、ディラック状態のみからなるp-n接合素子を作製し、p-n接合界面での電流とスピン流の振る舞いが明らかになることで、低散逸な電流/スピン流を利用した省エネ素子への展開が期待されます。

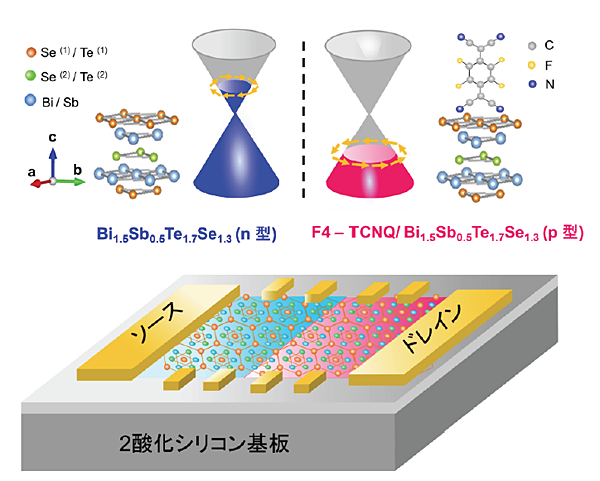

図1. 3次元トポロジカル絶縁体p-n接合素子の模式図。n型のBi1.5Sb0.5Te1.7Se1.3薄膜の一部領域に2,3,5,6-テトラフルオロ-7,7,8,8-テトラシアノ-キノジメタン(F4-TCNQ)分子を蒸着し電流の担い手を正孔(p型)に変換することによってp-n接合を作製した。

図2. (a)2酸化シリコン基板上に作製した3次元トポロジカル絶縁体Bi2-xSbxTe3-ySey p-n接合トランジスタの写真(b)p-n接合トランジスタの輸送現象。

用語解説

(*1)スピン流

スピン角運動量の流れのこと。例えば電子は電気的な自由度である電荷と、磁気的な自由度であるスピン角運動量を持っており、前者の流れを電流、後者の流れをスピン流と呼ぶ。

(*2)ディラック状態

今から約80年前に英国の物理学者ディラック(1933年ノーベル物理学賞)が提唱した相対論的効果を取り入れた「ディラック方程式」に従う粒子(ディラック電子)が存在する状態のこと。グラフェンや3次元トポロジカル絶縁体においては、この波動方程式における質量ゼロの場合と同様な、電子の運動量とエネルギーが線形の関係を持つ電子状態が観測される。

(*3)物理気相蒸着

物質表面に薄膜を形成する蒸着法のひとつ。本研究では、3ゾーン式管状型電気炉を用い、上流(高温)側に置いた原料を下流(低温)側に置いた基板上に蒸着することで薄膜を合成した。

(*4)電界効果トランジスタ

試料とゲート電極を隔てる様に絶縁体を配置し、ゲート電極に静電場を加えることで、試料のキャリア(電流を運ぶ担い手)の数を制御するデバイスの総称。

論文情報

"In-plane topological p-n junction in the three dimensional topological insulator Bi2-xSbxTe3-ySey"

(3次元トポロジカル絶縁体Bi2-xSbxTe3-ySeyの面内トポロジカルp-n接合)

"Ngoc Han Tu, Yoichi Tanabe, Yosuke Satake, Khuong Kim Huynh, Katsumi Tanigaki,

Nature Communications, 2016 (in press). (DOI 10.1038/NCOMMS13763)

お問い合わせ先

<研究について>

田邉 洋一(タナベ ヨウイチ)

東北大学大学院理学研究科物理学専攻 助教

TEL: 022-217-6173 E-MAIL: ytanabe[at]m.tohoku.ac.jp

<報道について>

皆川 麻利江(ミナガワ マリエ)

東北大学 原子分子材料科学高等研究機構(WPI-AIMR) 広報・アウトリーチオフィス

TEL:022-217-6146 E-MAIL: aimr-outreach[at]grp.tohoku.ac.jp

*[at]を@に置き換えてください

Posted on:2016年12月12日